本文介绍: 本文用于讲诉xilinx系列FPGA基于VIVADO的pin delay列表生成说明,以及一些注意事项,为FPGA设计人员探明道路。Pin delay 即FPGA内部die到pin的延时数据。

xilinx系列FPGA基于VIVADO的pin delay列表生成说明

1 概述

本文用于讲诉xilinx系列FPGA基于VIVADO的pin delay列表生成说明,以及一些注意事项,为FPGA设计人员探明道路。

Pin delay 即FPGA内部die到pin的延时数据。

2 示例平台

FPGA型号:xczu47dr-ffvg1517-2-i

Vivado版本:VIVADO 2022.2

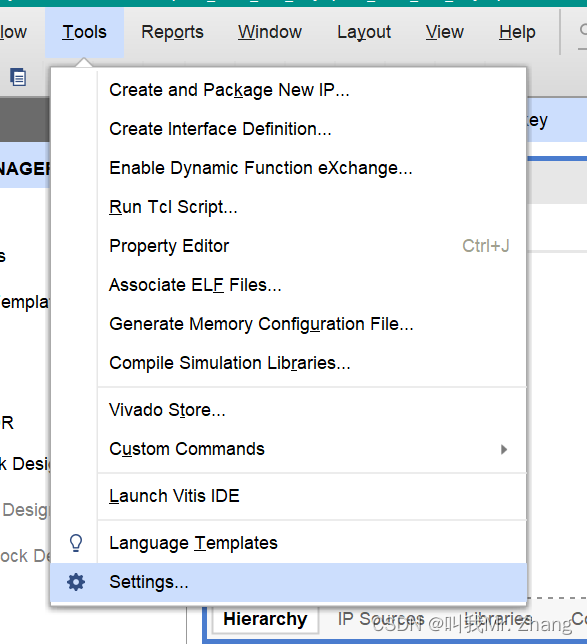

3 操作说明

1)打开vivado 找到tcl console输入命令窗口,输入命令:

(link_design –part xczu47dr-ffvg1517-2-i)

回车进入下一步;

4 注意事项

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。