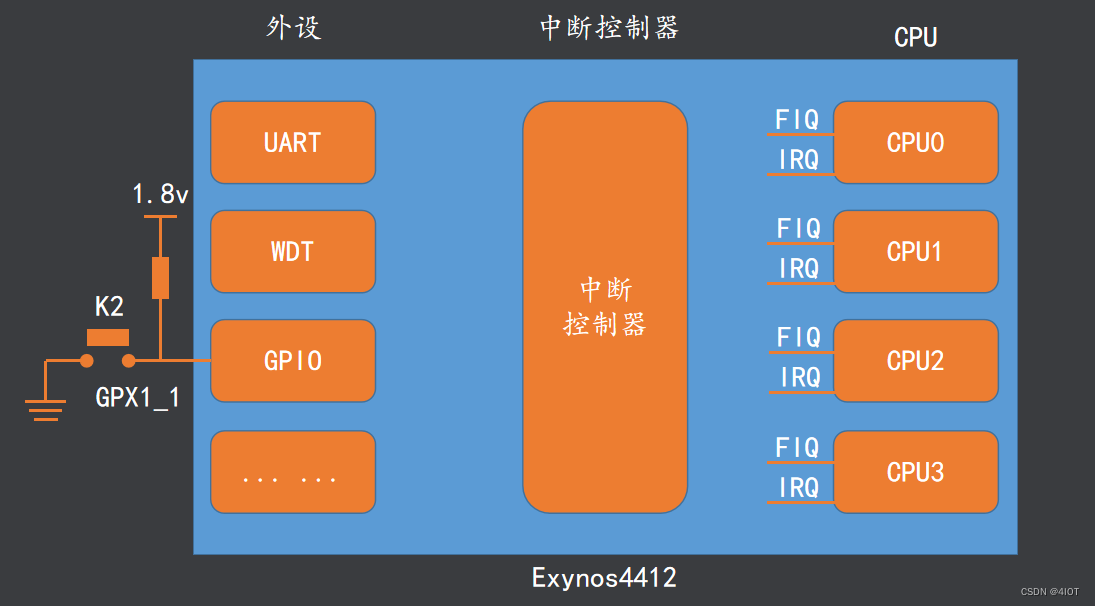

本文介绍: 中断控制器内容较多,只进行简单分析,实际开发很少去配置中断控制器,因为crotex-A系列处理,一般开发的时候会安装大型操作系统,操作系统内部会把中断控制器相关代码会实现好。控制指定CPU核心的中断控制器CPU接口的行为,包括使能和禁用中断处理、配置FIQ和IRQ中断的优先级等功能。ICDISER_CPU,25位置1,使能57号中断,使中断控制器接收到57号中断后能将其转发到CPU接口。ICCICR,使能中断控制器和CPU0之间的接口,使中断控制器转发的中断信号能够到达CPU0。

1 中断控制器

2 Exynos4412下的中断控制器

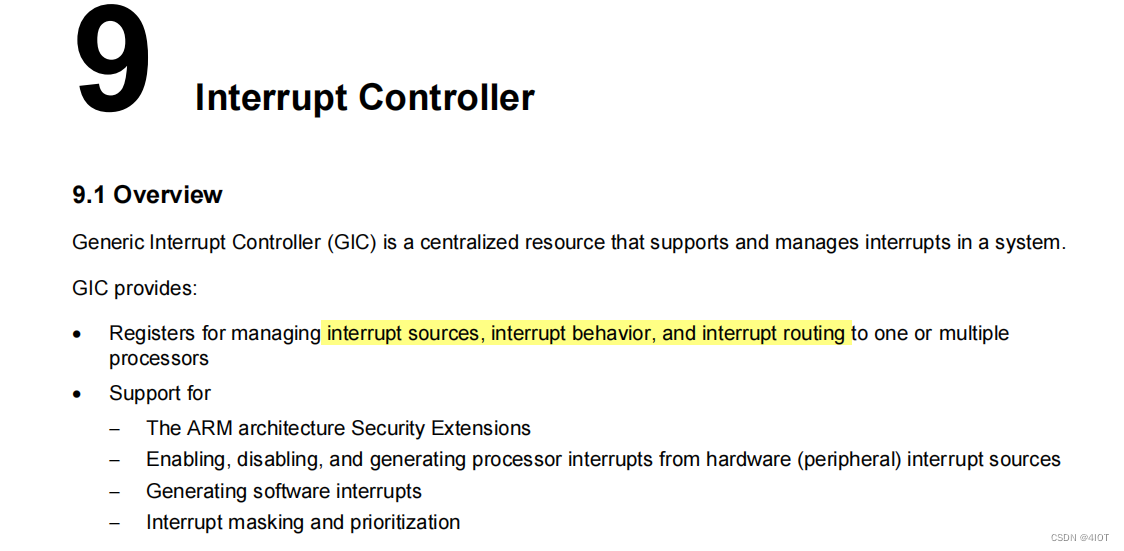

2.1 概述

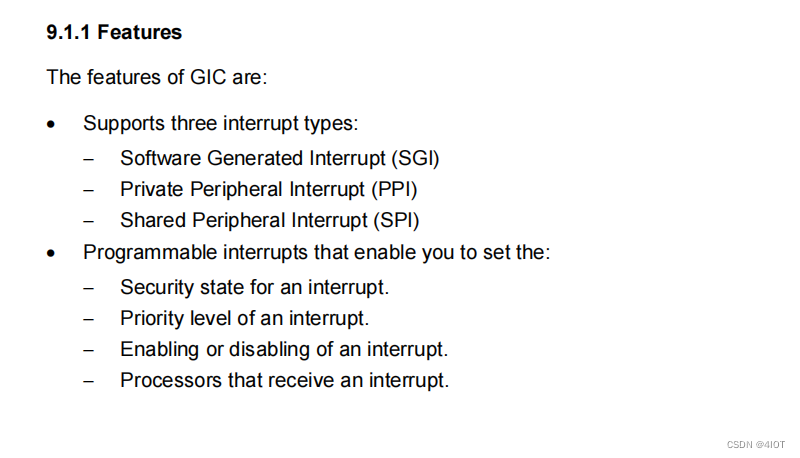

2.2 特征

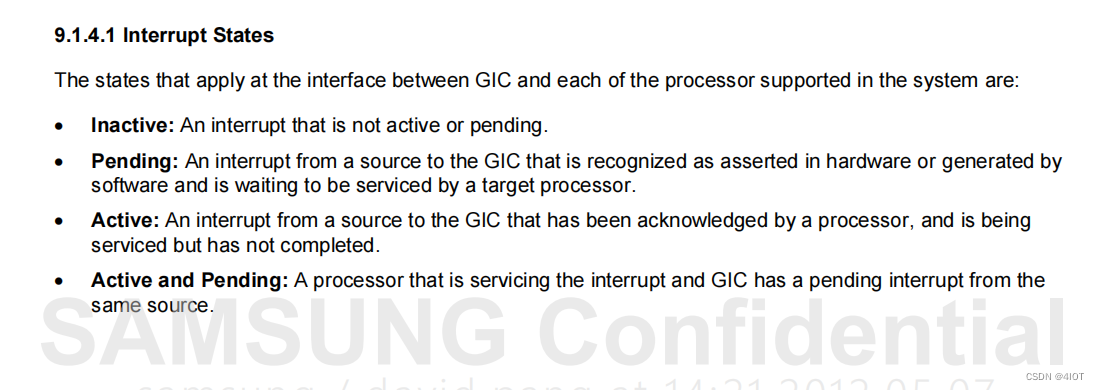

2.3 中断状态

2.4 中断类型

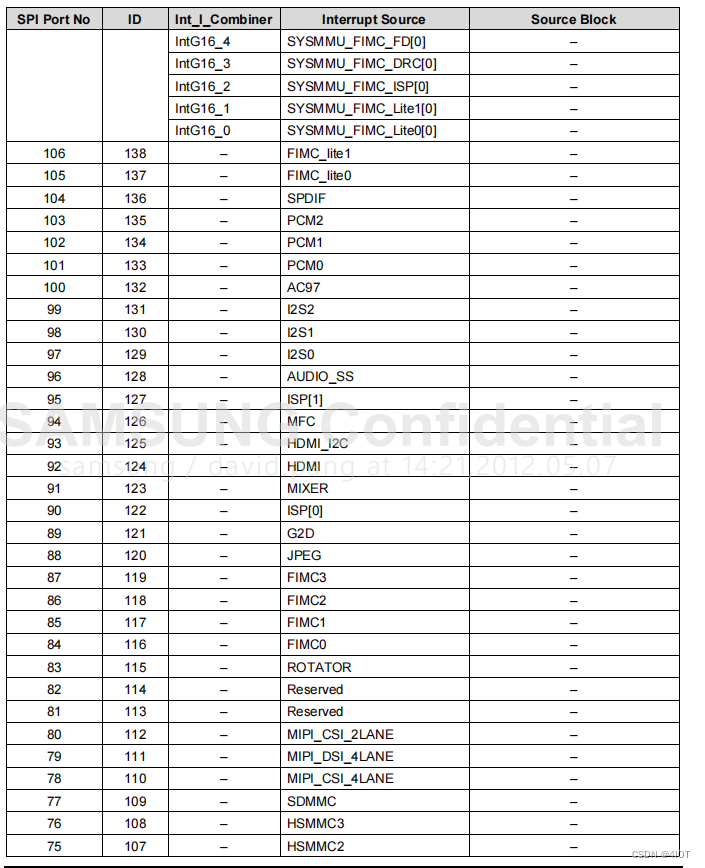

2.5 中断控制器GIC中断表

3 中断控制器寄存器详解

3.1 ICDDCR(Interrupt Controller Distributor Control Register)

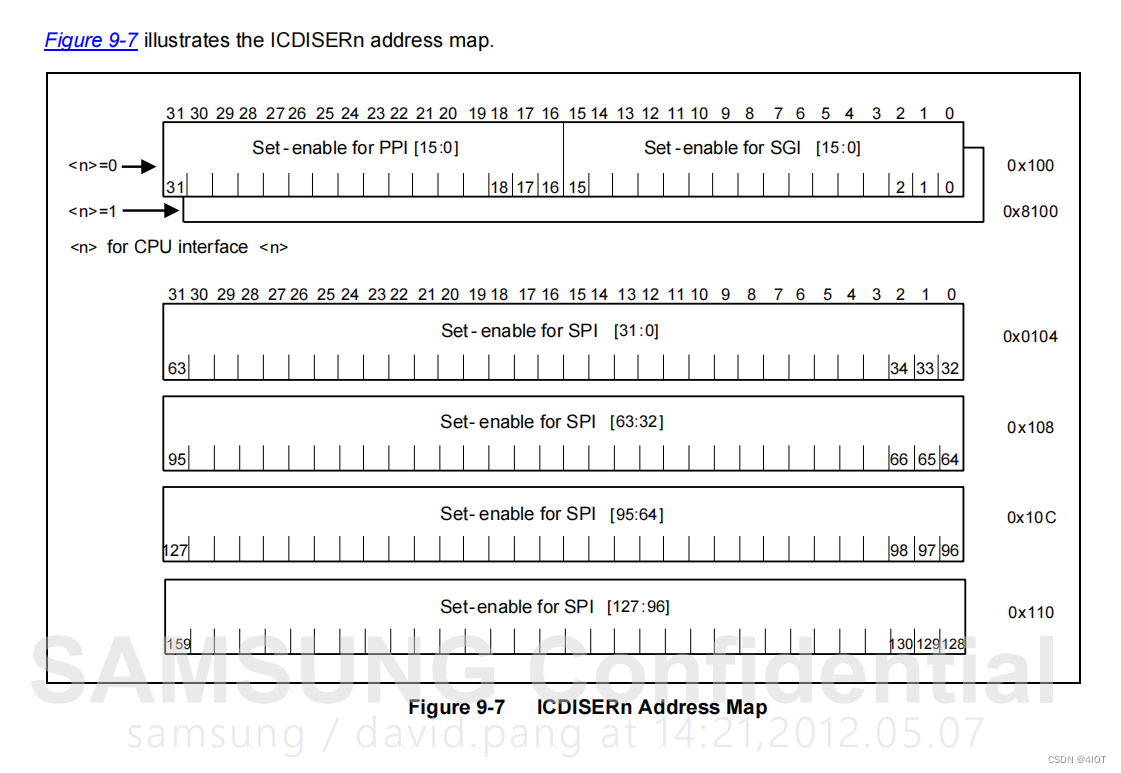

3.2 ICDISER_CPU(Interrupt Controller Distributor Set-Enable Register for CPU)

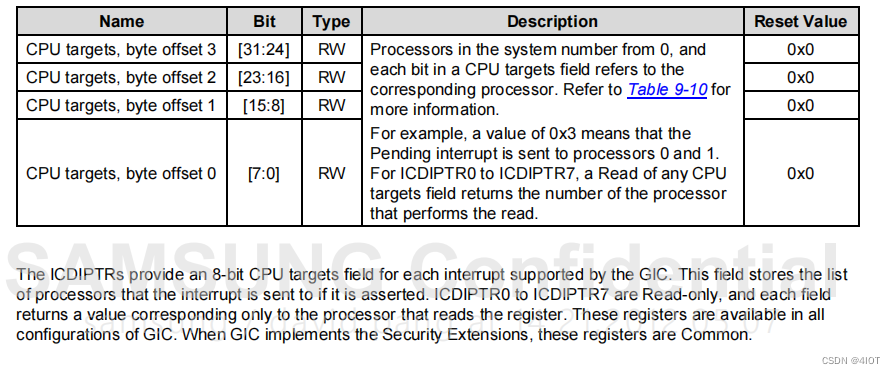

3.3 ICDIPTR_CPU(Interrupt Controller Distributor Interrupt Processor Targets Register for CPU)

3.4 ICCICR_CPUn(Interrupt Controller CPU Interface Control Register for CPU n)

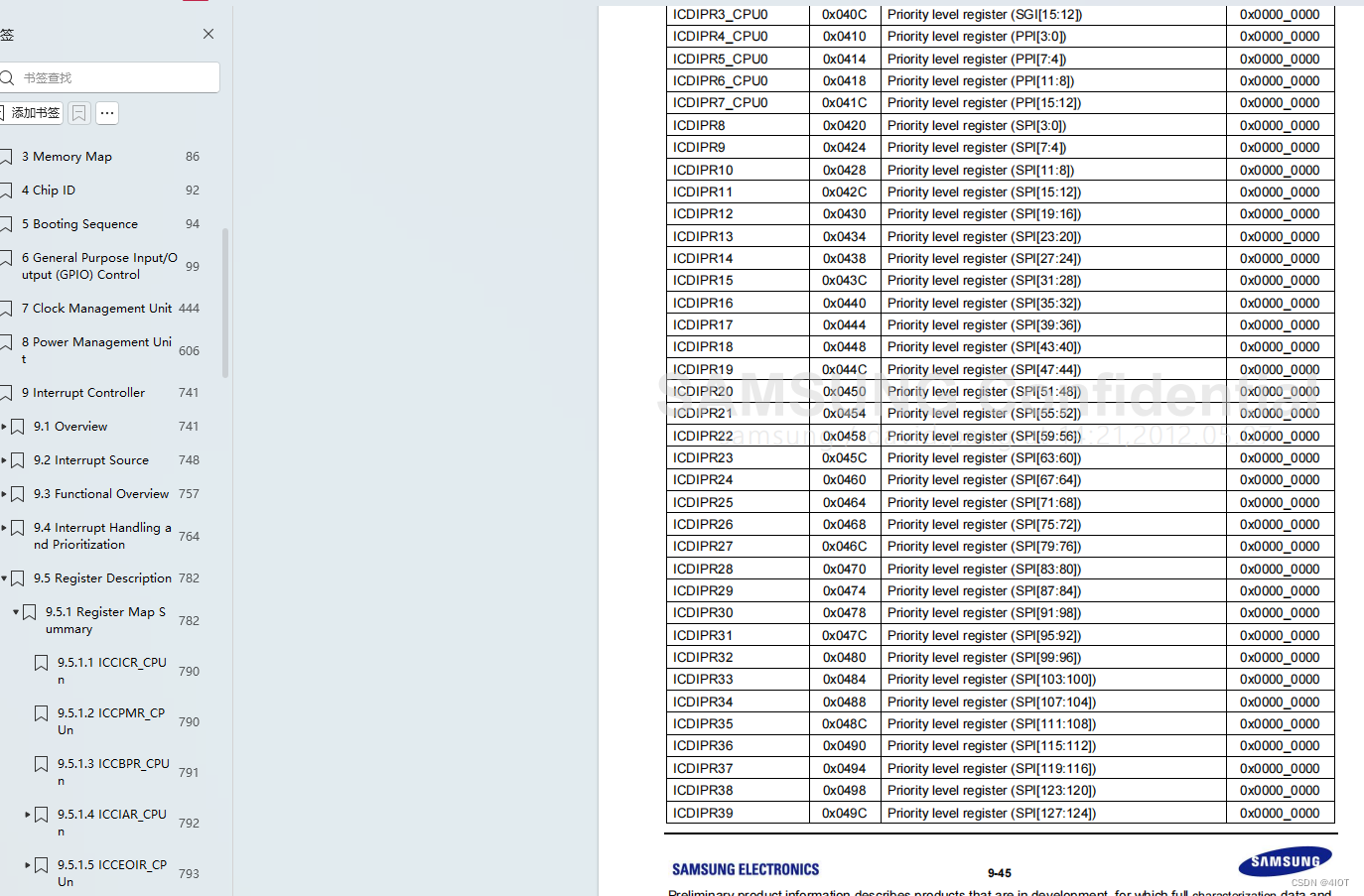

3.5 补充:中断控制器优先级设置寄存器

4 GPIO中断编程

4.1 外设层次设置

4.2 中断控制器层次设置

4.3 程序代码

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。

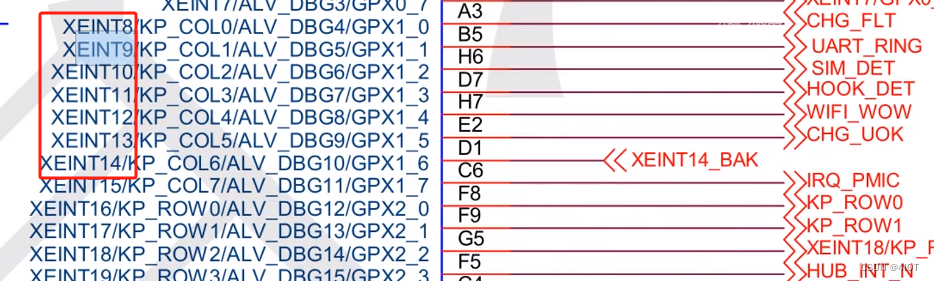

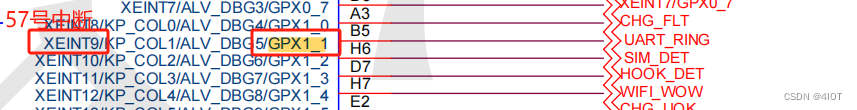

GPIO下降沿产生中断,

GPIO下降沿产生中断,

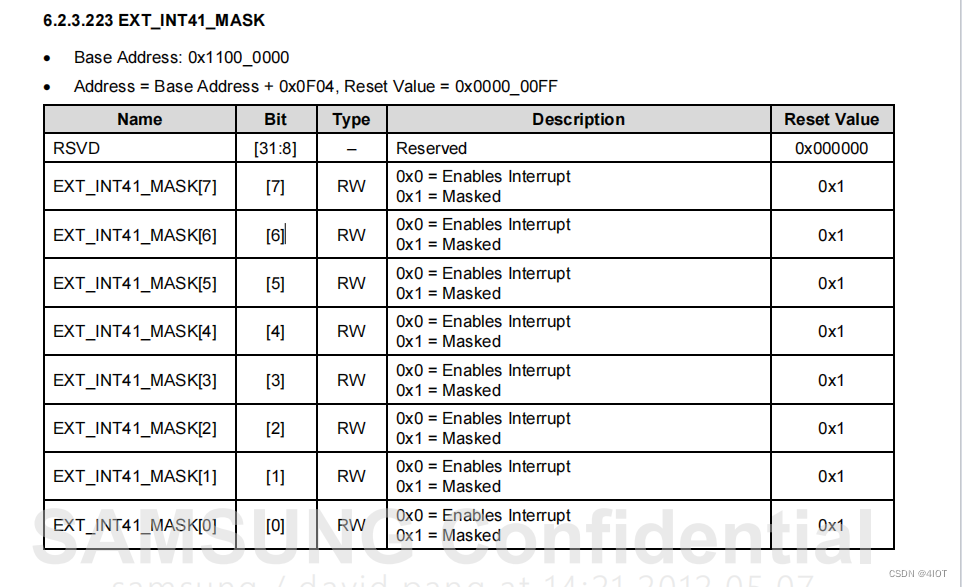

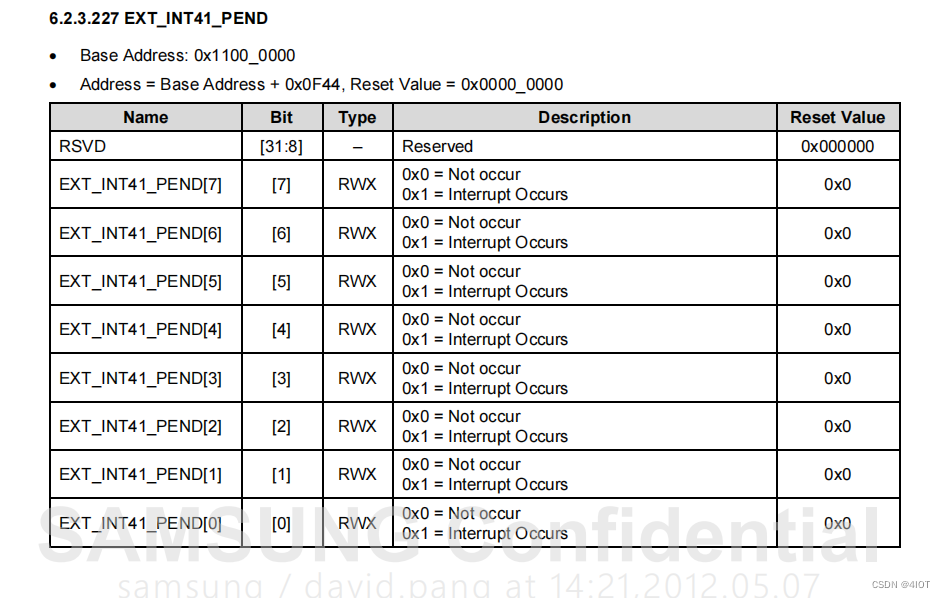

GPX与中断寄存器

GPX与中断寄存器