本文介绍: 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网根据时序图,数据是在第二个数据到来之后输出,当仅有一个数据到来时,不产生输出,所以内部需要一个指示信号valid_cnt,用来指示数据缓存状态。当data_lock内已缓存第一个数据时,valid_cnt拉高,当第二个数据到来后valid_cnt拉低endendendendendmodule。

专栏前言

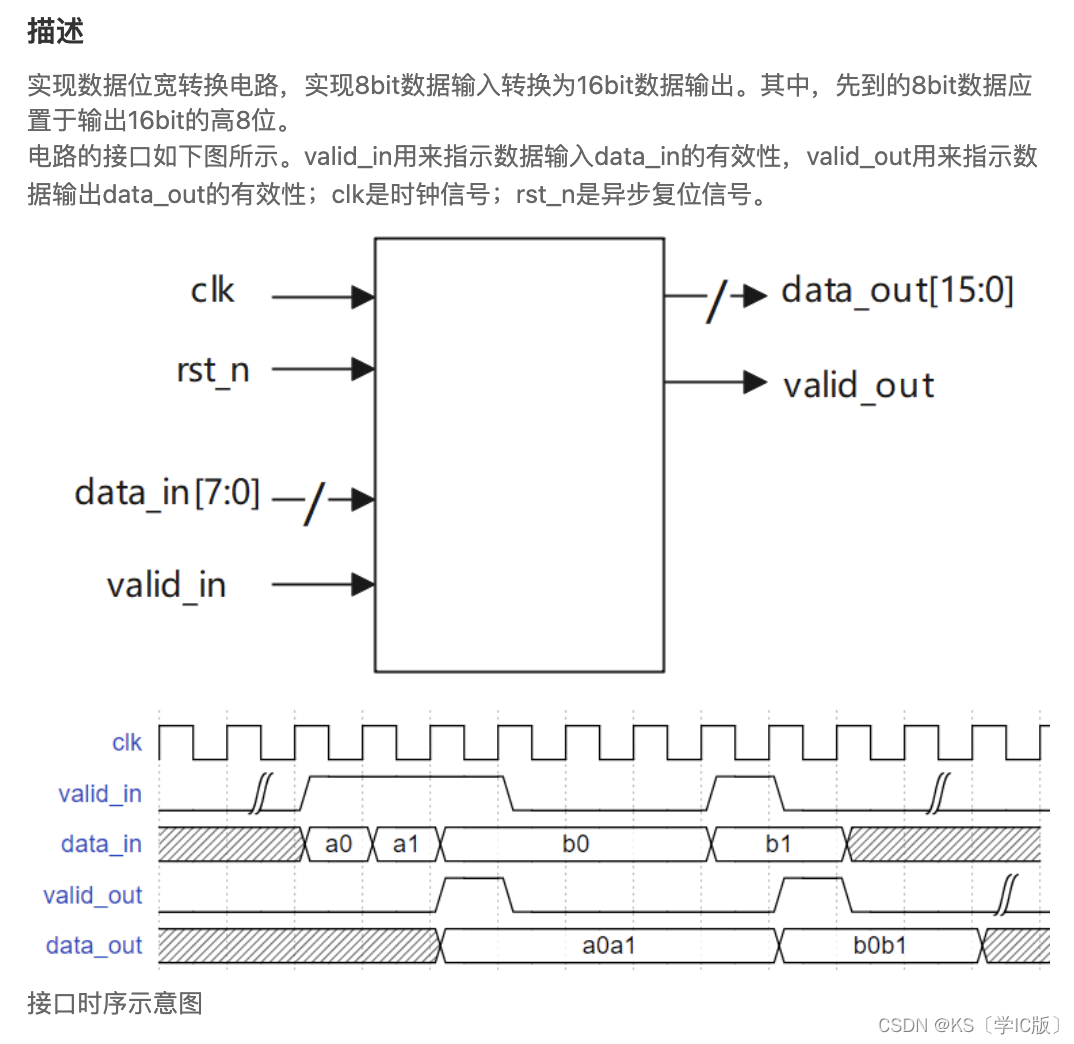

根据时序图,数据是在第二个数据到来之后输出,当仅有一个数据到来时,不产生输出,所以内部需要一个指示信号valid_cnt,用来指示数据缓存状态。当data_lock内已缓存第一个数据时,valid_cnt拉高,当第二个数据到来后valid_cnt拉低

`timescale 1ns/1ns

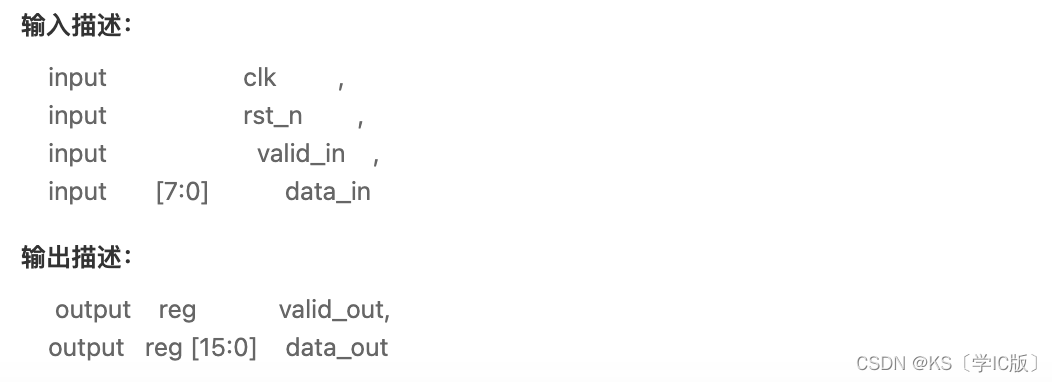

module width_8to16(

input clk ,

input rst_n ,

input valid_in ,

input [7:0] data_in ,

output reg valid_out,

output reg [15:0] data_out

);

reg [7:0] data_lock ;

reg valid_cnt ;

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) valid_cnt <= 'd0 ;

else if (valid_in) valid_cnt <= ~valid_cnt ;

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) data_lock <= 'd0 ;

else if (valid_in && !valid_cnt) data_lock <= data_in ;

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) valid_out <= 'd0 ;

else if (valid_in && valid_cnt == 1'd1) valid_out <= 1'd1 ;

else valid_out <= 'd0 ;

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) data_out <= 'd0 ;

else if (valid_in && valid_cnt == 1'd1) data_out <= {data_lock, data_in} ;

end

endmodule原文地址:https://blog.csdn.net/m0_54689021/article/details/134664318

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_25742.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。