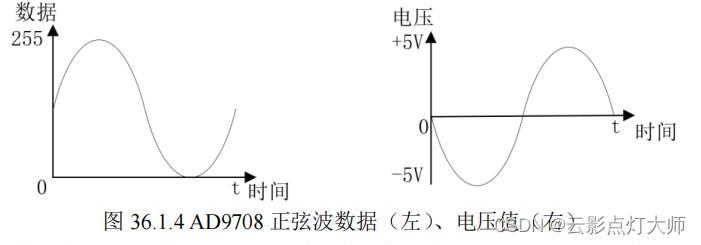

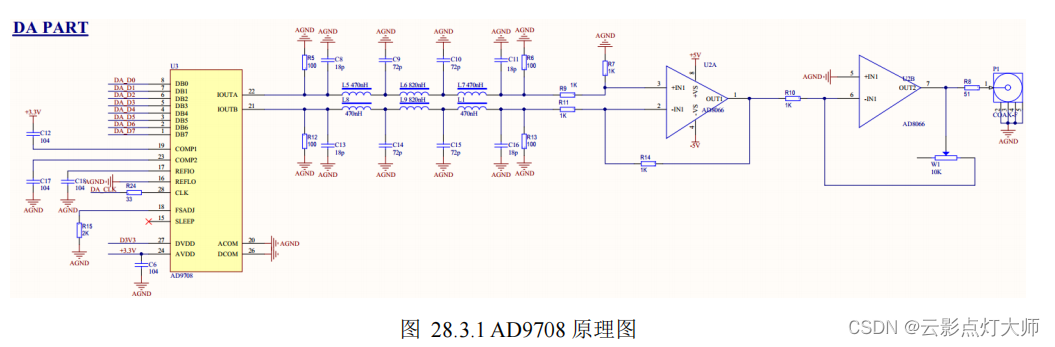

电路图:

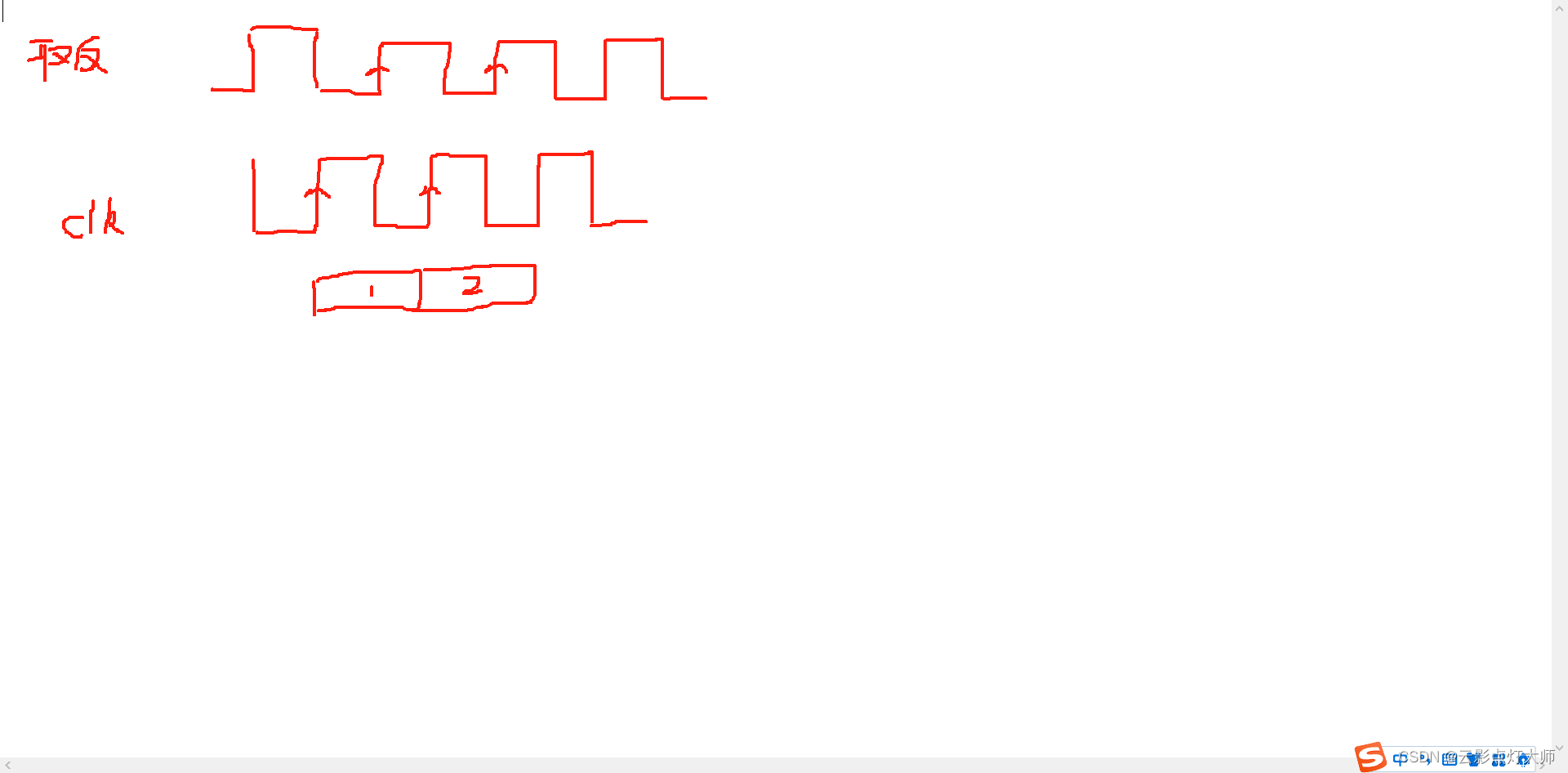

给DA转换器一个时钟,这个时钟是对clk时序时钟的取反。由于DA也是上升沿锁存数据,这样就保证DA模块读到的数据都是稳定了的数据。这样只是为了保证系统的稳定。

module da_wave_send(

input clk , //时钟

input rst_n , //复位信号,低电平有效

input [7:0] rd_data, //ROM读出的数据

output reg [7:0] rd_addr, //读ROM地址

//DA芯片接口

output da_clk , //DA(AD9708)驱动时钟,最大支持125Mhz时钟

output [7:0] da_data //输出给DA的数据

);

//parameter

//频率调节控制

parameter FREQ_ADJ = 8'd5; //频率调节,FREQ_ADJ的越大,最终输出的频率越低,范围0~255

//reg define

reg [7:0] freq_cnt ; //频率调节计数器

//数据rd_data是在clk的上升沿更新的,所以DA芯片在clk的下降沿锁存数据是稳定的时刻

//而DA实际上在da_clk的上升沿锁存数据,所以时钟取反,这样clk的下降沿相当于da_clk的上升沿

assign da_clk = ~clk;

assign da_data = rd_data; //将读到的ROM数据赋值给DA数据端口

//频率调节计数器

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

freq_cnt <= 8'd0;

else if(freq_cnt == FREQ_ADJ)

freq_cnt <= 8'd0;

else

freq_cnt <= freq_cnt + 8'd1;

end

//读ROM地址

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

rd_addr <= 8'd0;

else begin

if(freq_cnt == FREQ_ADJ) begin

rd_addr <= rd_addr + 8'd1;

end

end

end

endmodule

原文地址:https://blog.csdn.net/Treasureljc/article/details/134621643

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_41314.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!